FSM: Mealy

Fundamentals

- The output vector is a function of the state vector and the input vector: Y = f(X,S)

Three Processes

architecture RTL of MEALY is ... begin REG: -- Clocked Process CMB: -- Combinational Process with Next State Logic OUTPUT: process (STATE, X) begin -- Output Logic end process OUTPUT; end RTL;

Notes

Here, a Mealy automaton is shown.

The value of the output vector is a function of the current values of the state vector and of the input vector.

This is why a line is drawn in the block diagram from the input vector to the logic block calculating the output vector.

In the VHDL source code, the input vector is now listed in the sensitivity list of the corresponding process.

Mealy Example

architecture RTL of FSM_Mealy is subtype STATE_TYPE is std_ulogic_vector(1 downto 0); constant START : STATE_TYPE := "00"; constant MIDDLE : STATE_TYPE := "11"; constant STOP : STATE_TYPE := "01"; signal STATE,NEXTSTATE : STATE_TYPE; begin REG: • • • -- clocked STATE process CMB: • • • --Like Medvedev and Moore Examples OUTPUT : process (STATE, A, B) begin case STATE is when START => Y <= '0'; Z <= A and B; when MIDDLE => Y <= A nor B; Z <= '1'; when STOP => Y <= A nand B; Z <= A or B; when others => Y <= '0'; Z <= '0'; end case; end process OUTPUT; end architecture RTL;

Notes

In contrast to the other two types of automatons described before, the output values can not be simply written into the corresponding state bubble here.

Complete functions have to be written down which differ from state to state.

These functions are often “hidden” behind the state bubble, instead of explicitly displayed in the graphic.

In the VHDL source code, the calculation of the output values is described with concurrent signal assignments, again.

One can see that the input signals appear on the right side of the assignments and are therefore part of the output function, now.

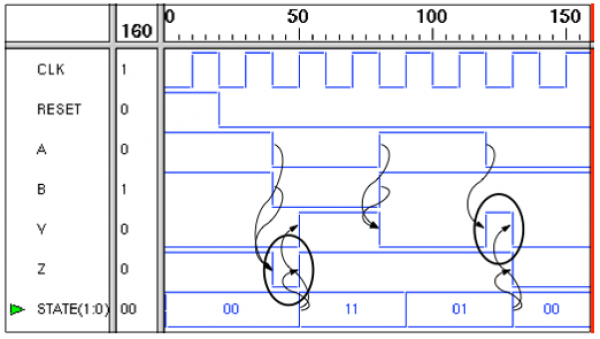

Waveform Mealy Example

- (Y,Z) changes with input ⇒ Mealy machine

- Note the “spikes” of Y and Z in the waveform

- FSM has to be modelled carefully in order to avoid spikes in normal operation.

Notes

Again, one can see the characteristics of the Mealy automaton clearly in the waveform.

The most remarkable feature is the fact that the output values change together with the values of the input vector, sometimes.

Furthermore, they change together with changes of the state vector values, of course.

As one can see, this can lead to so called spikes, i.e. signal pulses with a smaller width than the clock period.

This can lead to a misbehavior in the blocks following thereafter.

Of course, this has to be avoided and the designer must take special care when modelling a Mealy automaton in a form similar to the one described here.

Chapters of System Design > Synthesis > Finite State Machines and VHDL