Today's Development

Trend: Development of IC structure

Notes

Trend in IC development is System on Chip - a system consisting of tightly interacting hardware and software components using IP Cores to integrate them into new SoCs.

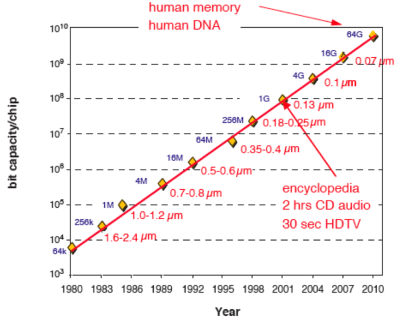

Moore's law: DRAM-Transistors on the Chip

- In 1965, Gordon Moore noted that the number of transistors on a chip doubled every 18 to 24 months.

- He made a prediction that semiconductor technology will double its effectiveness every 18 months

Notes

In the history of computer hardware there is a rule or observation (Moore’s law), that approximately every three years the next generation appears on the market with four times more memory capacity. The new technology allows smaller structures, the scaling factor for the internal feature size is always about 0.7

Empiric Observation of Gordon Moore (Intel founder) 1965 Additionally the complexity of the verification afford increases as well! (chart shows: Evolution in Complexity)

Moore’s Law in Action

Intel 4004 (1971)

- 2300 transistors

- 12 mm2 die

- 10 μm features

- 16 pins

- 108 kHz clock

- ~0.06 MIPS

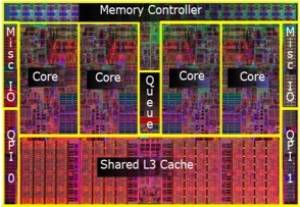

Intel Core i7 (2008)

- 731M transistors

- 263 mm2 die

- 45 nm features

- 1366 pins

- 3.2 GHz clock

- ~80 GIPS, 70 GFLOPS

Notes

- 256 KB L2 cache, 12 MB L3 cache

- TDP: 130W power consumption, (same as the i7 in 2008) 3.46 GHz

Relative measures

Intel Core i7 versus 4004

- 317,800 times as many transistors

- 22 times as much area

- 14,500 times as dense

- features are 222 times narrower

- 85 times as many pins

- clock runs 30,000 times as fast

- executes 1,333,333 times as many operations per second

- operations do more

Notes

Intel Core i7 Extreme Edition, introduction 11/2008: 3.2 GHz (3.73 GHz overclocked)

9 MB cache on chip

Today‘s Constraints

- Size (mobile phone, smart card, sensor technology)

- Reliability (automobile, other applications relevant to security)

- Savings in IC costs (consumer)

- Savings in Mounting and Connection technology (consumer)

- Savings in Power Dissipation (heat! cooling! battery lifetime!)

- Enhanced Functionality (number of inter-chip connections)

Notes

Today there are several constraints limiting the design of integrated circuits.

These differ according to the actual field of application.

A chip design for a mobile device will be constrained mainly by size and power dissipation, whereas an IC for automotive use needs to rather reliable than small.

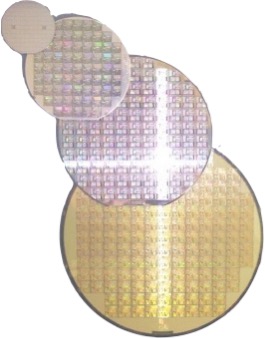

Levels of Integration

- SSI - Small Scale Integration (before 1960s)

- up to 100 GE per chip, chip 2 … 4 mm², feature size 10µm, 1’’- wafer

- MSI - Medium Scale Integration (1960s)

- up to 1000 GE per chip, 2’’- wafer

- LSI Large Scale Integration (1970s)

- up to 10.000 GE per chip, chip up to 100 mm², feature size 5 … 1 µm, 4’’- wafer

- VLSI Very Large Scale Integration (1980s)

- up to 100.000 GE per chip, 8’’- wafer

- ULSI Ultra Large Scale Integration (1990s - now)

- up to 1 Mio GE per chip, 12”-wafer, chip up to 400 mm², feature size 0,8 … 0,25 µm

- SoC and WSI Wafer Scale Integration (future)

- more than 1.000.000 GE/macros/cores on one slice , 1 … 4’’- wafer

Notes

GE== gate-equivalents or even a core or macro cell (WSI)

(MSI:) The next step in the development of integrated circuits, taken in the late 1960s, introduced devices which contained hundreds of transistors on each chip, called “Medium-Scale Integration” (MSI).

Up to today the integration enhanced up till now (ULSI) to hundred of millions of transistor on each chip and up to several millions of GE on one chip.

Problem: Design Gap

Solution:

- “programmable“ ICs (processors, µC, application specific: ASIC)

- standardized design tools

- extensive library concepts + prefab (half-finished) chips ⇒ mask-programmable ASICs, Structured ASICs

Notes

This chart is showing a trend in Productivity: the number of available gates in a chip rises faster than the ability to reasonably design (use) them. Which means, the Complexity of a chip outpaces design productivity more and more seriously.

The Problem of Design Productivity

Development of Design Productivity:

- But…

- How to design chips with more and more functions?

- Design engineering population does not double every two years…

- Hence, more efficient design methods are needed!

- Productivity of development has to be raised, yet it stays behind the increase of chip complexity (21 %/year)

- Efficient organization of the development has top priority

- Work on the highest level of abstraction

- Automation by applying efficient algorithms

Hardware Description Languages

Chapters of System Design > VHDL - Overview and Application Field > Application Field of HDLs