Concepts of VHDL

Execution of assignments

- Sequential

- Concurrent

Methodologies

- Abstraction

- Modularity

- Hierarchy

Notes

VHDL distinguishes itself from other languages by the way assignments are executed because two basic types of statements are known:

- Sequential statements are executed one after another, like in software programming languages. Subsequent statements can override the effects of previous statements this way. The order of the assignment must be considered when sequential statements are used.

- Concurrent statements are active continuously. So the order of the statements is not relevant. Concurrent statements are especially suited model the parallelism of hardware.

VHDL features also three important modelling techniques:

- Abstraction allows for the description of different parts of a system with different amount of detail. Modules which are needed only for the simulation do not have to be described as detailed as modules that might be synthesized.

- Modularity enables the designer(s) to split big functional blocks and to write a model for each part.

- Hierarchy lets the designer build a design out of submodules which may consist of several submodules, themselves. Each level of hierarchy may contain modules of different abstraction levels. The submodules of these models are present in the next lower hierarchical level.

Abstraction

- Abstraction is hiding of details:

- Differentiation between essential and nonessential information

- Creation of abstraction levels:

- On every abstraction level only the essential information is considered, nonessential information is left out

- Equality of the abstraction:

- All information of a model on one abstraction level contains the same degree of abstraction

Notes

Abstraction is defined as the hiding of information that is too detailed. It is therefore necessary to differentiate between essential and non-essential information. Information that is not important for the current view of the problem will be left out from the description. Abstraction levels are characterized by the kind of information that is common to all models of this level.

A model is said to be of a certain abstraction level if every module has the same degree of abstraction. If this is not the case than the model will be a mixture of different abstraction levels.

Abstraction Levels in IC Design

Notes

The four abstraction levels of a digital circuit design are shown in the figure. The functional description of the model is outlined in the behavioral level. There is no system clock and signal transitions are asynchronous with respect to the switching time. Usually, such descriptions are simulatable, only, but not synthesizable.

In the next step, the design is divided into combinational logic and storage elements. This is called the Register Transfer Level (RTL). The storage elements (Flip Flops (FFs), latches) are controlled by a system clock. In synchronous designs, FFs should be used (driven by the edge of the clock signal) exclusively, because transparent latches (driven by the level of a control signal) are not spike-proof. For the description on RT level only 10 to 20 percent of all VHDL language constructs are needed and a strict methodology has to be followed. This description on RT level is called synthesizable description.

On the logic level, the design is represented as a netlist with logic gates (AND, OR, NOT, …) and storage elements. The final layout is at the bottom of the hierarchy. The different cells of the target technology are placed on the chip and the connections are routed. After the layout has been verified, the circuit is ready for the production process.

Except for the layout part all the abstraction levels can be covered with VHDL.

Abstraction Levels and VHDL

Notes

VHDL is applicable to the upper three abstraction levels. It is not suitable to describe a layout. The design entry in behavioral and RT level is usually done by text editors. Graphical tools are also available but experienced users often find it easier to write the code by hand. On the gate level, a schematic is modified as VHDL netlist descriptions tend to become too complex pretty soon.

The transition from an upper abstraction level to a lower one is supported more or less efficiently by software.

Behavioral synthesis is still a dream of many researchers as only very simple behavior models are synthesizable. A common application is the design of RAM cells for the target technology, where only the generic parameters (width, depth, number of ports, (a)synchronous, …) need to be specified.

Logic synthesis, however, has been perfected in recent years. As long as the designer confines himself to certain simple VHDL constructs that are sufficient for RT level descriptions, the synthesis tools will be able to reproduce the behavior in the logic level.

As a result of the ongoing research in efficient place and route algorithms the step from the logic level to the final layout has been widely automated for digital standard cell designs.

Description of Abstraction Levels

Notes

In the behavior level, complete systems can be modelled. Bus systems or complex algorithms are described without considering synthesizability. The stimuli for simulation of RTL models are described in the behavior level, for example. Stimuli are signal values of the input ports of the model and are described in the testbench, sometimes called validation bench.

The designer has to take great care to find a consistent set of input stimuli that do not contradict the specification. The responses of the model have to be compared with the expected values which, in the simplest case, can be done with the help of a waveform diagram that shows the simulated signal values.

On the RT level, the system is described in terms of registers and logic that calculates the next value of the storage elements. It is possible to split the code into two blocks (cf. process statement) that contain either purely combinational logic or registers. The registers are connected to the clock signal and provide for synchronous behavior. In practice, the strict separation of Flip Flops from combinational logic is often annulated and clocked processes describe the registers and the corresponding update functions.

The gate netlist is generated from the RT description with the help of a synthesis tool. For this task, a cell library for the target technology which holds the information about all available gates and their parameters (fan-in, fan-out, delay) is needed.

Based upon this gate netlist the circuit layout is generated. The resulting wire lengths can be converted into propagation delays which can be fed back into the gate level model (back annotation). This allows for thorough timing simulations without the need for additional simulator software.

Behavioral Description in VHDL

o <= transport i1 + i2 * i3 after 100 ns;

Notes

A simple specification of the function of a module is shown. The output o depends upon the three input values i1, i2 and i3. Furthermore it is specified that a new output value must be stable at the latest 100 ns after the input values have changed.

In a behavioural VHDL description, the function can be modelled as a simple equation (e.g. i1 + i2 * i3) plus a delay of 100 ns. The worst case, i.e. that 100 ns are needed to calculate a new output value, is assumed here. So behavioural means in fact the behaviour of the design in time.

RT Level in VHDL

Notes

In VHDL functional behavior is modelled with so called processes. Two different types of processes exist in RT level descriptions: the pure combinational process and the clocked process. All clocked processes infer FlipFlops and can be described in terms of state machine syntax.

In addition to the data input and data output signals, the control signals like the module clock (CLOCK) and reset (RESET) for asynchronously resetable FlipFlops have to be considered in modelling on RT level. When a synchronous reset strategy is employed, the reset input is treated like an ordinary data input.

It follows that RT level VHDL code also contains some sort of structural information in addition to the functional behavior as storing and non-storing elements are separated. Timing issues in form of when signal values may be updated (e.g. synchronously to the clock signal) are also considered.

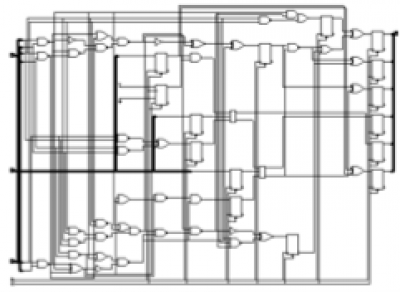

Gate Level in VHDL

U86 : ND2 port map (A => n192, B=> n191, Z=> n188); U87 : ND2 port map (A => I3_2, B=> I2_0, Z => n175); U88 : ND2 port map (A => I2_2, B=> I3_0, Z => n173); U89 : NR2 port map (A => mul_36_PROD_not_0, B=> n174, Z => n185); U90 : EN port map (A => n181, B=> n182, Z => n180); U91 : ND2 port map (A => I3_2, B=> I2_1, Z => n181); U92 : ND2 port map (A => I2_2, B=> I3_1, Z => n182); U93 : IVP port map (A => n180, Z => n192); U94 : A06 port map (A => n173, B=> n174, C => n175, Z => n172); U95 : NR2 port map (A => n174, B=> n173, Z => n176); U96 : ND2 port map (A => I3_1, B=> I2_1, Z => n174); U97 : EN port map (A => n183, B=> n178, Z => product64_4); U98 : ND3 port map (A => I2_2, B=> I3_2, C => n174, Z => n183);

Notes

A VHDL gate level description contains a list of the gates (components) that are used in the design. Another part holds the actual instantiation of the components and lists their interconnection.

A schematic of the gate structure of a digital circuit can be seen on the left side of the picture. The right side shows a part of the corresponding VHDL description. Each single element of the circuit (e.g. U86) is instantiated as a component (e.g. ND2) and connected to the corresponding signals (n192, n191, n188). All used gates are part of the selected technology library where additional information like area, propagation delay, capacity, etc. is stored.

Information Content of Abstraction Levels

Notes

The behavior model is a simple way to describe the behavior of a circuit, similar to usual software programming languages, such as PASCAL or C. With this description, only the functional behavior can be simulated by a VHDL simulator.

The clock pulse is the distinguishing mark for the RT level description. All operations are related to the clock signal. RT level simulations give no information about the real timing behavior, which means that is impossible to tell, whether all signals have actually settled to stable values within one clock period or not.

When the model is described on the logic level, delays can be applied to the used gates for simulation. The timing information is part of the synthesis library. This enables a rough validation of the timing behavior. The uncertainty stems from the propagation delay along the signal wires which has not yet been considered. These delays may very well make up the main part of the entire delay in larger designs.

If the layout is completed, the wire lengths and thus the propagation delays will be known. The design can be simulated on gate level with the additional delay values and consequently the timing behavior of the entire circuit can be validated. Yet, the simulation time grows considerably with the increased amount of information about the circuit, which restricts timing simulation to small parts of complex designs.

Modularity and Hierarchy

- Partitioning in several partial designs

- Restrict complexity

- Enable teamwork

- Study of alternative implementations

- Soft macros

- Simulation models

Notes

Modularity allows the partitioning of big functional blocks into smaller units and to group closely related parts in self-contained subblocks, so called modules. This way, a complex system can be divided into manageable subsystems. The guidelines for partitioning can differ from design to design. Most of the time functional aspects are considered as partitioning constraint. The existence of well defined subsystems allows several designer to work in parallel on the same project as each designer will view his part as a new, complete system.

Hierarchy allows to build a design out of modules which themselves may be built out of (sub-) modules. One level of a hierarchical description contains one ore more modules that can even have different degrees of abstraction. Possibly existing submodules are present the next lower hierarchical level.

Modularity and hierarchy help to simplify and organize a design project. Additional advantages are that different implementation alternatives can be examined for the modules, e.g. in a simulation. Only the corresponding component instantiation needs to be changed for this in the overall model. Also analogues interfaces can be modelled in VHDL and added to the system model for simulation. Sometimes, simulation models of the devices that will be connected to the new design exist and can be used for a simulation of the design under test in its real working environment.

Chapters of System Design > VHDL - Overview and Application Field