Code Examples

Door opener, combinational

| VHDL | Verilog |

|---|---|

library ieee; use ieee.std_logic_1164.all; entity DoorOpener is port (C, H, P : in std_logic; F : out std_logic); end DoorOpener; architecture beh of DoorOpener is begin process (C, H, P) begin F <= not(C) and (H or P); end process; end beh; | module DoorOpener(C, H, P, F); input C, H, P; output F; reg F; always @(C, H, P) begin F <= (~C) & (H | P); end endmodule |

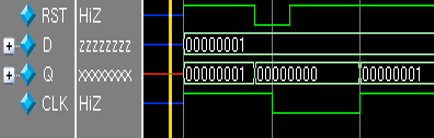

D-FF, variable width, sequential

| VHDL | Verilog |

|---|---|

library IEEE; use IEEE.std_logic_1164.all; entity DFF is generic (Width : natural); port ( CLK : in std_logic; RST : in std_logic; D : in std_logic_vector(Width-1 downto 0); Q : out std_logic_vector(Width-1 downto 0)); end entity DFF; architecture RTL of DFF is begin -- DFF with asynchr. low-active reset DFF : process (CLK, RST) begin if (RST = '0') then Q <= (others => '0'); elsif rising_edge(CLK) then Q <= D; end if; end process DFF; end architecture RTL; | module DFF (CLK, RST, D, Q); parameter Width = 8; input CLK, RST; input [Width-1:0] D; output [Width-1:0] Q; reg [Width-1:0] Q; // DFF with asynchr. low-active reset always @(posedge CLK or negedge RST ) begin: DFF // block Name if (~RST) begin Q = 0; end else Q = D; end endmodule even shorter … module DFF (CLK, RST, D, Q); parameter Width = 8; input CLK, RST; input [Width-1:0] D; output [Width-1:0] Q; reg [Width-1:0] Q; // DFF with asynchr. low-active reset always @(posedge CLK or negedge RST) if (~RST) Q = 0; else Q = D; endmodule |

Chapters of System Design > VHDL vs. Verilog